Power Supply Subsystem

The XP2 Brevia Board is powered by an AC adapter connected on J6 jack. The AC adapter converts the AC voltage to a 6V, 1 A DC voltage. This DC input is then fed into two National LM117 voltage regulators. According to the LM117 data sheet, the out voltage ranges from 1.2 to 37 at 1.5 A and is configurable using resistors in the output feedback loop. The output is computed using the following equation:

Vout = Vref (1 + R2/R1) + Iadj*R2

As per the data sheet, Vref is a fixed 1.25 V, and Iadj is a small fixed current. In the equation above, the Iadj part is small enough to be ignored for practical purposes. For the 1.2 V output, “R2” is R22, a zero ohm resistor, and thus the output voltage is equal to Vref. This is within the tolerance of the FPGA core voltage, the input voltage required to power the core parts of the FPGA: the LUTs, flip-flops, mux, etc. that make up the logic cells.

For the 3.3 V output, “R2” is R24 and “R1” is R23. R2/R1 is 1.65, which when added to 1 and multiplied by Vref provides about 3.3V volts. This 3.3V is actually Vio, the voltage required for the FPGA input and output pads. Most FPGAs usually have two voltage supplies: the core and I/O voltages. FPGAs with high speed serial transceivers–SERDES–often have a separate supply for these transceivers.

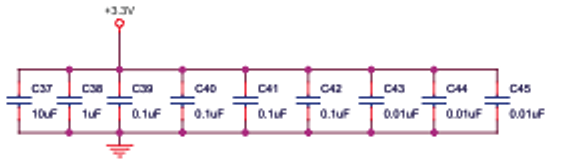

On the schematic also note the capacitors C26-C32 and C37-C45 placed respectively between the 1.2V and 3.3V regulated output and ground. C27-C45 are shown below as in the schematic.

These are decoupling capacitors, usually inserted between an IC voltage input and ground so that when the IC draws large currents and the voltage supply level temporarily drops, the capacitors discharge their stored energy in and effort to keep the voltage level constant. The capacitors are often drawn this way in industry so as not to clutter the schematic near the ICs. This style does make it easier for FPGA, micro-controller, or microprocessor developers to focus on the I/Os around the device.

Another interesting section of the schematic on the page with the DC regulators is the ground-ground connection:

Often this is a notation to mark that the digital and analog ground planes are to be joined by a connection so that both analog and digital share the same ground plane.

Clock Subsystem

A 50 MHz square wave output oscillator (select the H22/H32/H53/SWO datasheet), X1, is on the circuit board and will act as the reference clock in the FPGA. The output of the oscillator, XOUT, is directly connected to the FPGA and there is not really anything interesting in this clock subsystem, except for C8 attached between the XOUT signal and ground. C8 is a load capacitor, and for more information on load capacitors on the output of an oscillator, consult the manufacturer’s technical note Effect of Load Capacitance on the Crystal.

We will do more with the clock signal once we start working with the innards of the FPGA.

Global Reset Subsystem

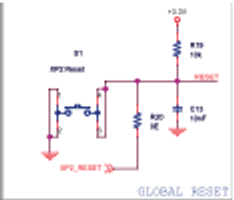

The XP2 board has a reset push-button, S1, that when pushed resets the FPGA to an initial state. The circuit for the reset is shown below:

The circuit attached to the output of the push-button S1 is a simple analog debouncing circuit. A debounce circuit is necessary because it prevents spurious noise from accidentally resetting the system. Conceptually, the debounce circuit is very easy to understand. When 3.3V is supplied and the push-button is depressed, the RESET and signal is a logical ‘high’ or ‘1’ value, and capacitor C13 begins to charge. Remember that the time required for the capacitor to discharge is roughly 5*T, where T=R19*C13. When the push button is pressed it causes the current from 3.3V to travel the path of least resistance to ground. In other words, the RESET signal is pulled-down to ground. Capacitor C13 resists voltage changes, and starts to discharge its stored energy in an futile attempt to keep the voltage levels the same. After about 5*T, the capacitor will be completely discharged and RESET sits at ‘low’ or ‘0’ value. The following is a simple SPICE (MacSpice) model that shows the level of RESET: the switch is initially open, and then at t=1ms the push-button is pressed and held down.

* Analog Switch Debouncing

* Use a pulse to emulate the behavior of an analog switch pulling-down input voltage

V1 1 0 PULSE(0 3.3 2ns 2ns 2ns 1ms 2ms)

R1 1 2 10k

C1 2 0 10n ic=0

.control

tran .005 .002 uic

plot v(2)

.endc

.end

V(2) is the equivalent of the RESET signal in the circuit schematic above.

Because the push-button must be depressed longer than 5*T, sudden spikes and instantaneous signals on the RESET line will not cause the FPGA to be reset. For this circuit, under ideal circumstances, T=10k*10nF=100us, and 5*T is 500us. For modern FPGAs and digital circuits, 500us is an eternity! Only a purposeful reset will make its way to the FPGA. Note also that the signal XP2_RESET is connected to RESET by a zero ohm resistor R20. XP2_RESET goes to the external connector J4 pin 39 so that an FPGA on one board will travel to any external connections to J4. XP2_RESET can be disabled by removing R20 from the circuit board if desired.

Conclusion

Now that we understand the power, clock and reset sub-systems, we are ready to begin experimenting with the FPGA itself. The next step is to setup the clock and reset signals inside of the FPGA.